CSAPP Chapter6

这篇笔记将记录我在ICS课上学习CSAPP第六章The Memory Hierarchy的过程。已完结。

The Memory Hierarchy

Memory Hierarchy

Memory

RAM:基础存储单元是一个cell,一个cell存储一个bit。

- Static RAM:更稳定、更快、更贵

- Dynamic RAM:需要持续充电保证内部状态稳定

SRAM和DRAM都是volatile memories,断电后数据会丢失。

ROM:nonvolatile memories,断电后数据不会丢失。

Firmware:存储在ROM中的程序,可编程。

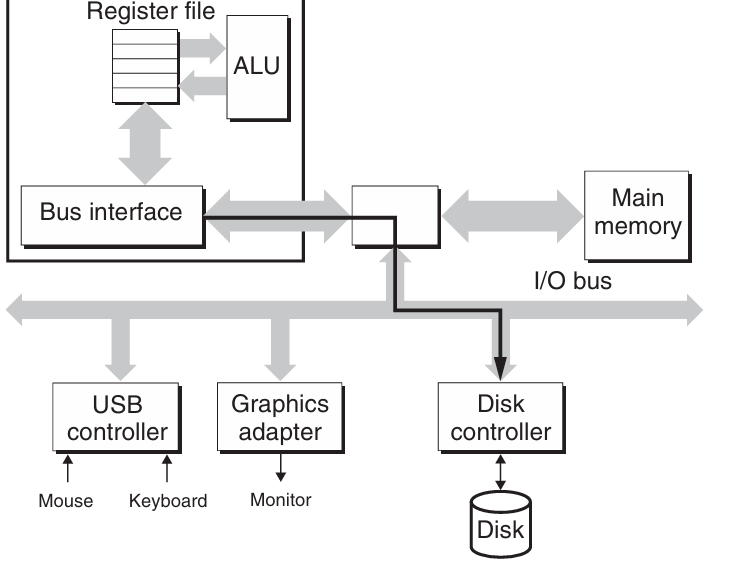

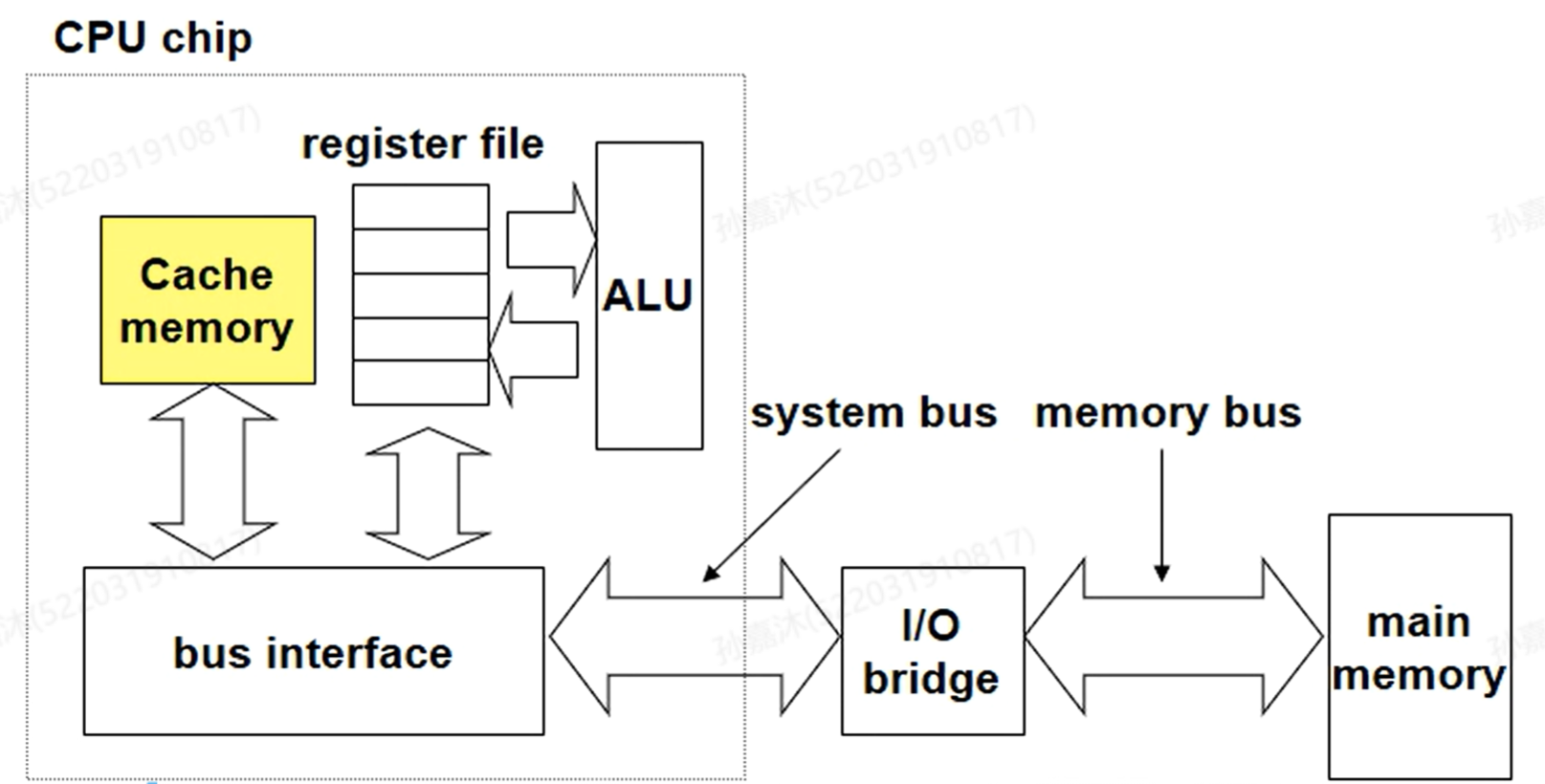

CPU和memory通过bus连接起来。

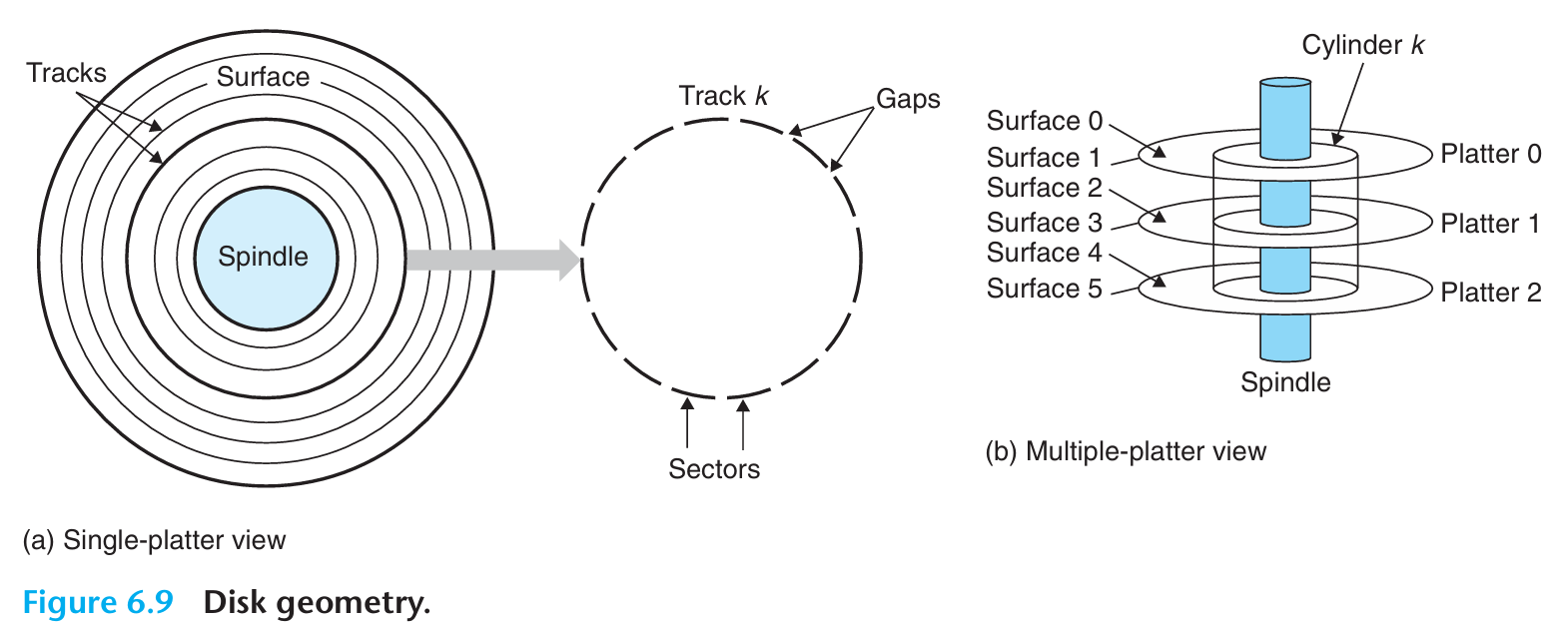

Disk

一个platter有两个surface,一个surface上有很多track,每个track会切成一个个间隔开的sector。

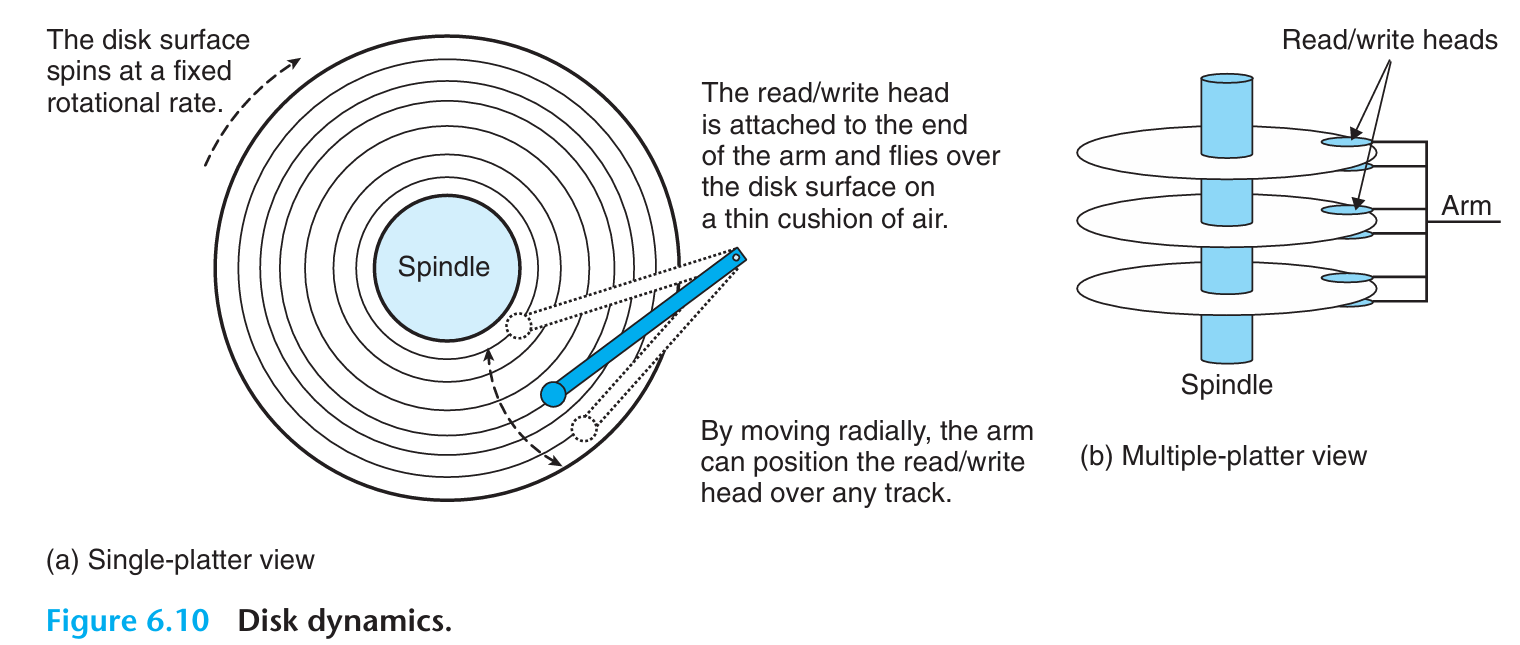

磁盘自身会旋转,手臂的head在不同track之间移动。

Memory-mapped I/O

内存映射区域:I/O设备映射到地址空间的一部分区域。

CPU访问这部分区域,通过总线向外部设备的port发送读写指令。

通常CPU会进行异步I/O,将后续事情交给disk controller来做。磁盘通过DMA将数据从磁盘写入memory。当DMA transfer完成后,disk controller会通过中断通知CPU的pin(引脚)。

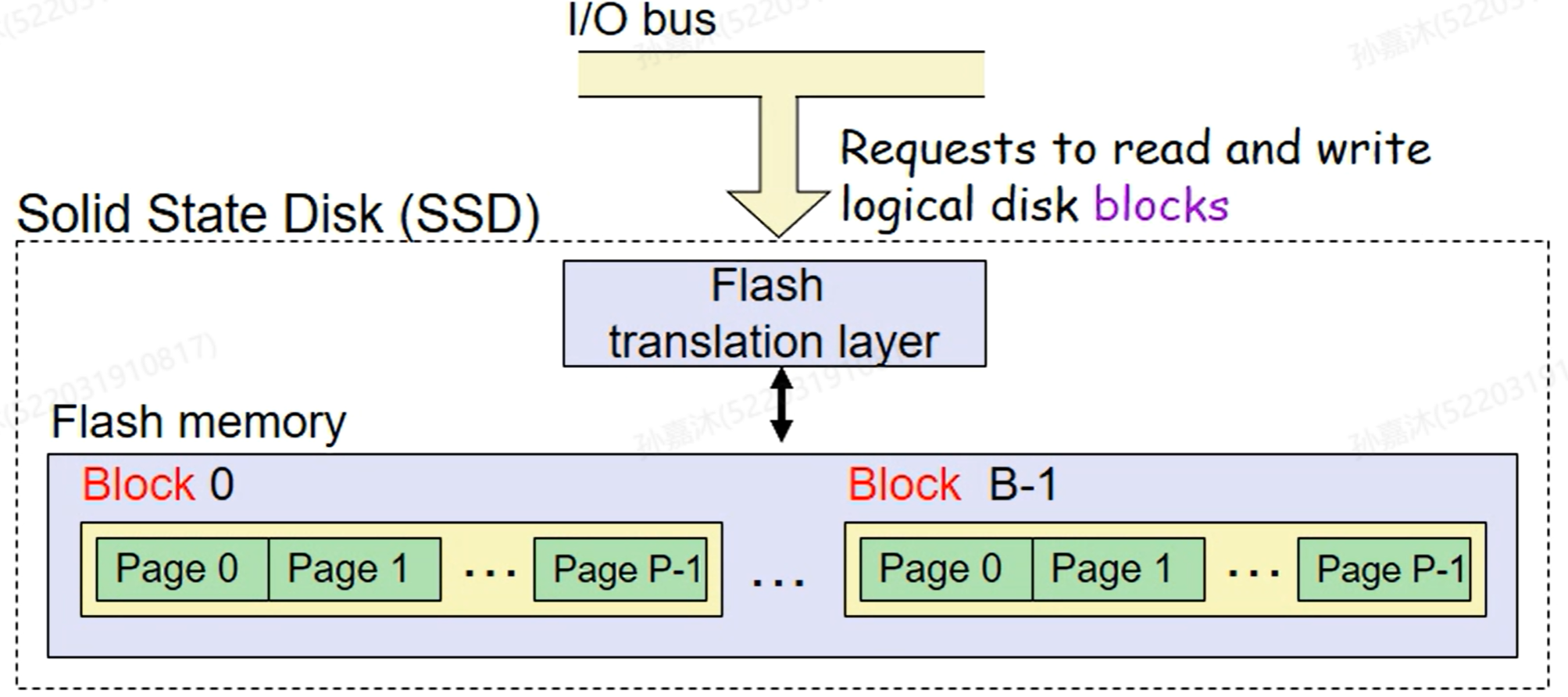

Solid State Disk (SSD)

– 基于flash memory

– Flash translation layer = disk controller

一个page只能写一次,重新写要先擦掉。一次性会擦掉一整个block(因为擦除操作开销很大)。

一个block重复写多次(100000次)后会wear out。

顺序读写很快 随机写很慢。

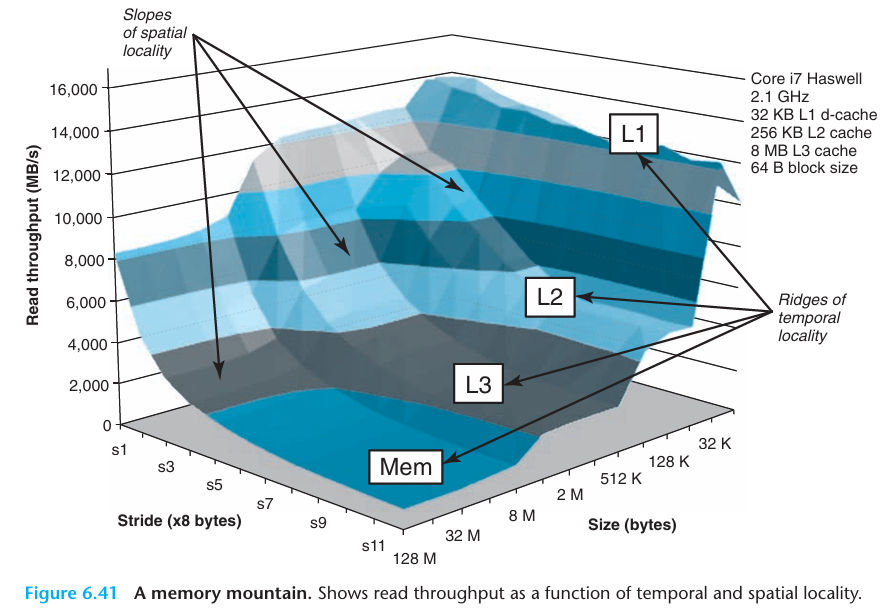

Locality

- Temporal locality(时间局部性)

最近被访问的数据,倾向于很快会再次被访问。

- Spatial locality(空间局部性)

访问的数据临近的其他数据,倾向于会一起访问。

Caches

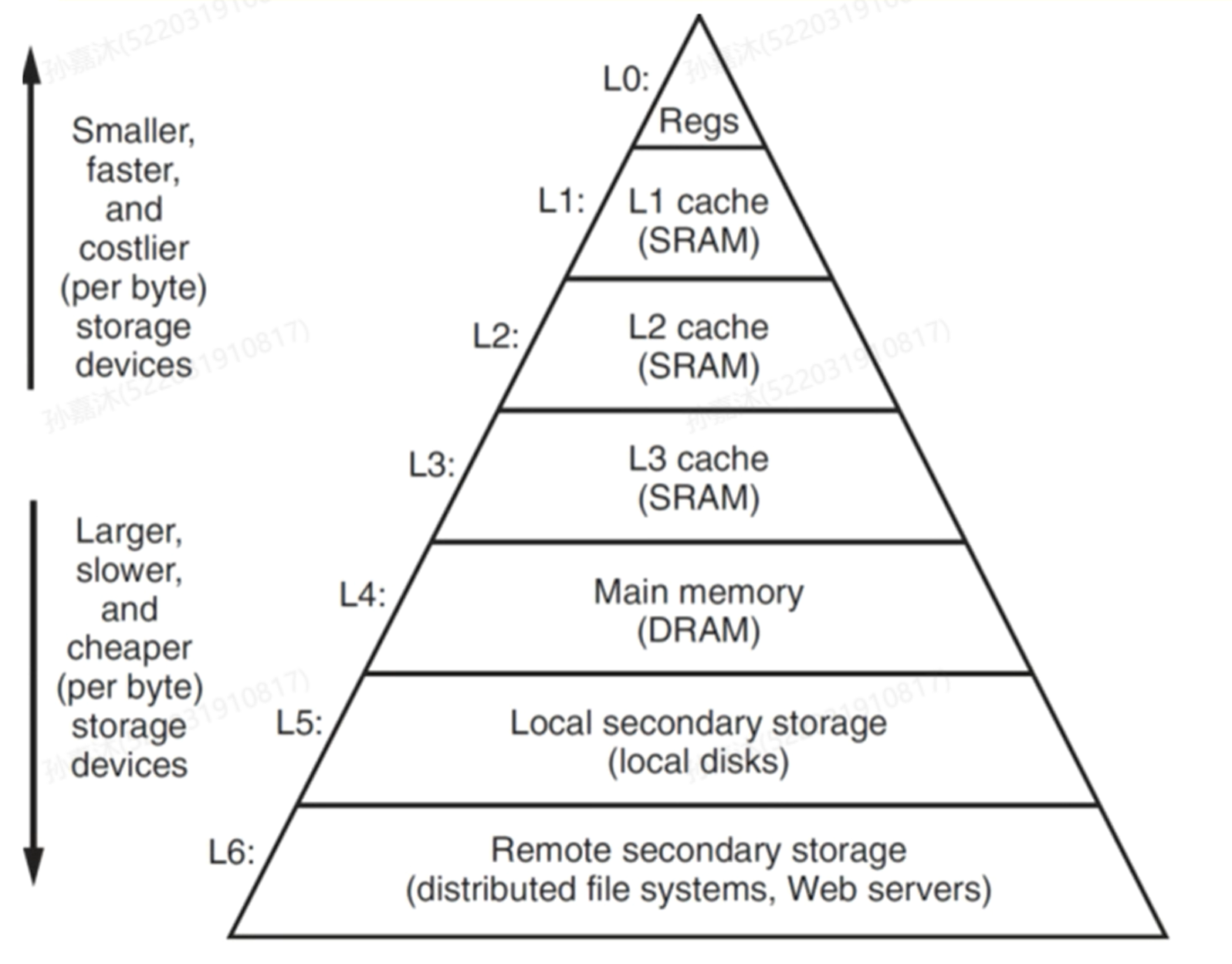

金字塔的越上面越小、越快、越贵。

每个上面一层都是下一层的cache。

Cache Misses:

- Cold miss:cache为空

- Capcity miss:cache已满

- Conflict miss:cache中有空间,但是有多个数据映射到cache的相同位置,与硬件设计相关

Cache Memory在CPU芯片上:

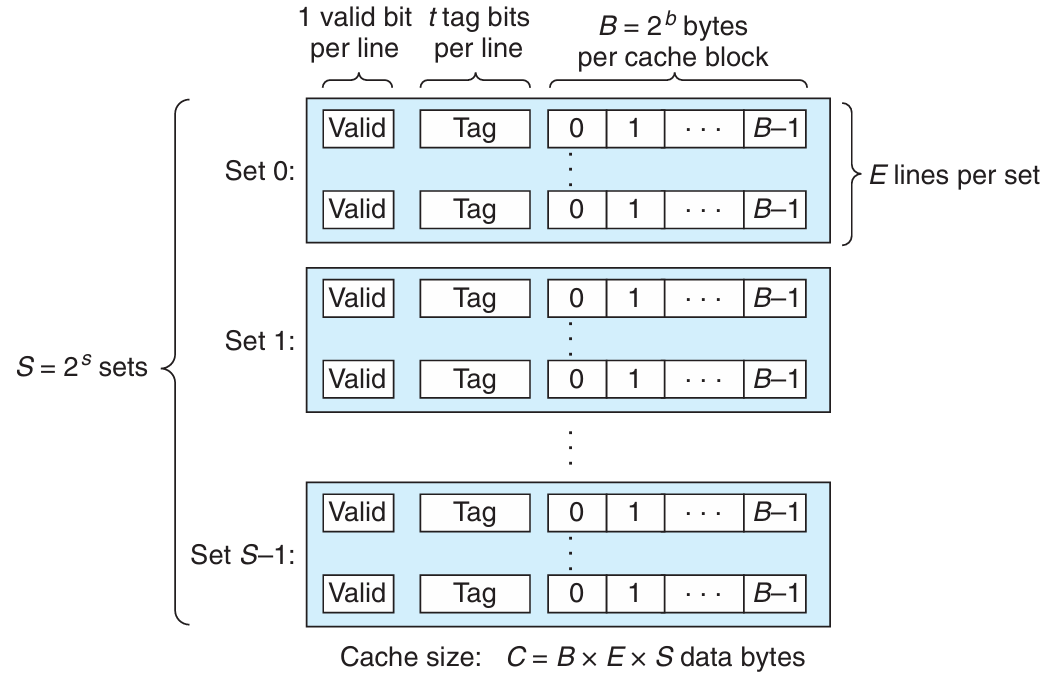

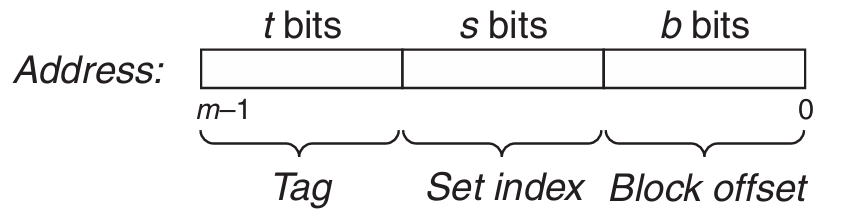

Generic Cache Memory Organization

Cache由一组set组成,每个set包含一条或多条line。

先通过set index确定set,然后匹配tag,最后访问block offset:

Direct-mapped cache: 一个set只包含一条line。L1 cache最早会用这种设计。速度较快,但是thrashing(conflict)会比较严重。

Set associative cache: 一个set包含多条line,line match的时候一起匹配。

越上层的cache的associate越小。

Line Replacement on Misses

如何选择要驱逐的line?

-

LFU (least-frequently-used)

-

LRU (least-recently-used)

Write cache-friendly code

有better locality的程序会有较低的miss rate。